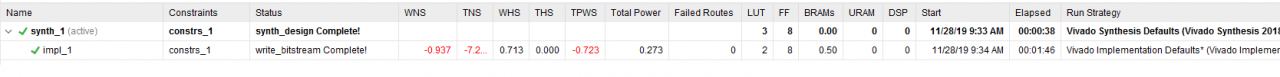

Today, when we do a simple MCU read-write experiment of Bram in FPGA, the experiment is very successful at low frequency. When we increase the frequency from low frequency to 552.96mhz through PLL, we find that vivado prompts the following information:

Run “report”_ “Timing” or “report”_ timing_ After the “summary” command, you will notice WNS, TNS, WHS, and ths.

WNS stands for worst negative slack

TNS represents the total negative slack, that is, the sum of the paths of negative timing margin.

Whs stands for worst hold slack

Th represents the total hold slack, that is, the sum of the paths with negative hold slack.

These values tell the designer the difference between the design and timing requirements. If it is a positive value, it means that the timing requirements can be met; if it is a negative value, it means that the timing requirements cannot be met.

But it doesn’t mean that the time sequence warning function can’t be realized, it’s just that the project is unstable. There will be problems if you add or delete modules or even recompile them. At this time, you can open implementation to see the location of the timing warning.

The so-called timing can not meet the requirements means that it can not meet the establishment and maintenance time, so we should pay attention to the timing constraints.

I ignored these warning messages and continued to download them to the board. As a result, the experiment was successful.

I guess: if the logic code of FPGA is enlarged, there will be a problem.

Read the full text

Copyright belongs to the author

Report

Reward

0 like

0 collection

microblog

share

Other popular articles by the author

Spring AOP intercepts method invalidation in abstract class (parent class)

Npoi user manual

The debug hub core was not detected and data read from HW_ ila [hw_ ila_ 1] is corrupted…

NDK string processing getstringutfchars

Similar Posts:

- android.graphics.Bitmap.Config

- Quartz: add transaction rollback error [How to Solve]

- [How to Solve] directory not found for option

- Springboot uses the Datetimeformat (pattern = “yyyy MM DD HH: mm: SS”) annotation to automatically convert the string to date type error

- InternalError: cudaGetDevice() failed. Status: CUDA driver version is insufficient for CUDA runti…

- Solution to the cache problem of JVM DNS

- Send QQ e-mail message prompt: error in certificate certificate is not trusted

- [Solved] StarRocks Error: close index channel failed/too many tablet versions

- [Solved] Django error: AttributeError: ‘QuerySet’ object has no attribute ‘id’

- How to solve the problem of “no such BSSID available” when handling 5GHz frequency band WiFi by using air play ng